TWEPP ’07 reviewed lessons learnt and looked to future projects.

The Topical Workshop on Electronics for Particle Physics (TWEPP ’07) recently brought together more than 160 participants from the international high-energy physics community, specialized technical institutes and industry. Held in Prague on 3–7 September 2007, the workshop was organized by Charles University, the Czech Technical University, the Institute of Physics and the Nuclear Physics Institute of the Czech Academy of Sciences. It represented both a continuation and a significant broadening of the scope of the series of annual Workshops on Electronics for LHC Experiments initiated in 1994.

Image credit: H Pernegger/CERN.

This series of workshops began within the framework of the R&D programme supervised initially by CERN’s Detector Research and Development Committee and later by the LHC Committee. The goal was to promote collaboration and dissemination of relevant expertise within the LHC community, harness specialized knowledge from industry and technical institutes and encourage common approaches and the adoption of standards. The proceedings of the previous 12 workshops show that the programme met these aims. Overall progress has often been spectacular, from the initial R&D phase to the installation and commissioning of the large-scale and complex high-technology electronics systems for LHC experiments. Despite the successful resolution of the many initial R&D challenges, several practical electrical engineering aspects have recently proved to cause some of the biggest headaches in assembling the full LHC detector systems.

With the LHC experiments now well into their commissioning phase, the meeting in Prague was a timely occasion to review lessons learned from more than a decade of design, production and installation of detector electronics. It was also a time to look forward to the challenges of developments in electronics for potential experimental facilities beyond the LHC, such as the Super-LHC (SLHC), the International Linear Collider (ILC) and the Compact Linear Collider study, as well as neutrino and fixed-target experiments. The workshop featured 89 submitted presentations, nine invited talks, topical sessions on supply and distribution of power in detectors, working groups on microelectronics and optoelectronics, and an optional tutorial on robust ASIC designs for hostile environments. While the majority of contributions (58%) described electronics for LHC experiments, 9% of the papers addressed an SLHC upgrade issue and 33% concerned the ILC or other experiments. Some 16% of participants were from non-European institutes.

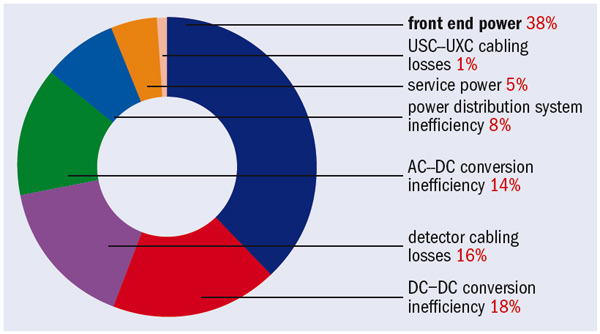

Data: S Lusin/Fermilab.

Some lessons learnt

Approximately 40% of the workshop contributions were on electronics systems, installation and commissioning. This is no surprise given the advanced state of the LHC experiments. Speakers reported on significant progress in integrating the sub-detectors in the LHC experiments and in commissioning tests with cosmic rays. In general, the performance of the front-end and back-end electronics and the associated software and firmware for controls, monitoring and readout, agrees well with expectations. This major achievement is largely a result of the tremendous effort that the community has made to deliver complex and functional electronics systems to the experiments. However, installation and verification of the complicated services for the front-end electronics (power, cooling, cables etc) often turned out to be much more difficult than anticipated. One particular point of concern relates to the supply and distribution of power to the experiments. In the current LHC detectors, typically only around 30–40% of the power produced is really dissipated in the front-end circuits, the remainder being lost in long power cables and through conversion inefficiencies in power supplies.

A more efficient power distribution system would have reduced the amount of material required in the form of power cabling and cooling infrastructure to remove the heat; this in turn would have allowed improved tracking detectors. The development of such power supply and distribution systems will be critical for the successful construction of future detectors. In a possible SLHC luminosity upgrade, for example, a 10-fold increase in luminosity will require detectors with higher granularity and hence an increased number of electronic channels. The use of advanced front-end ASIC technology holds the promise of reduced power dissipation per channel, and therefore should help to contain any increase in the global power dissipation of the whole front-end electronics systems. Nevertheless, these advanced IC technologies operate at lower voltages than those employed in the LHC detectors today, so the fraction of power dissipated in power cabling at the SLHC detectors is at risk of increasing.

To review the present situation and discuss future orientations, the workshop devoted a day to topical sessions on power management and distribution in large detector systems, with presentations and discussions about several new approaches. At the ILC for instance, the time structure with bunch trains of around 1 ms interspersed with 200 ms of idle time offers the possibility of placing the electronics in quiescent mode during the idle periods, which could lead to a 99% reduction in the average power consumed by the front-end electronics. This power cycling technique cannot be used at the SLHC, but local DC–DC conversion and serial powering are strong alternative options. The first of these alternative approaches delivers power to the front-end modules at high voltage (say, 24 V) and then uses a local DC–DC converter to step down to the required ASIC supply voltage (1.5 V for 130 nm CMOS). In the serial-powering approach the floating modules are powered in series and fed with a constant current. Each module is equipped with a voltage regulator and a current shunt in order to maintain the required drop in supply voltage, regardless of load variations or possible module failure.

The topical sessions concluded with general agreement on the need to adopt a coordinated approach to the supply, management and distribution of power for large experiments in order to avoid a posteriori systems engineering. A working group will be established to assess power-related issues, including lessons learnt from LHC detectors; power management developments required for future upgrades and experiments; and methodologies for the quality control and qualification of power systems.

Front-end to back-end

The second largest session of the workshop focused on ASIC developments. In view of the considerable challenge presented by electronics for the future SLHC or ILC detectors, clear signs of vigorous development activity are excellent news. The ASIC session covered a rich set of applications, including front-end circuits for pixel and micro-strip detectors for tracking, front-end electronics for calorimetry at the LHC, SLHC and ILC, and generic functions, such as single-event upset-tolerant programmable logic and optical transfer of data, clock and trigger signals at multi-gigabit rates. ASIC projects presented at the workshop employed a range of standard CMOS technologies (with minimum feature sizes of 350 nm, 250 nm, 180 nm and 130 nm), as well as other technologies chosen to meet the specific requirements of different detectors. The latter included silicon-germanium processes to handle signals with a wide dynamic range, high-voltage processes for DC–DC converter developments, and silicon-on-insulator technology for the development of monolithic integrated pixel detectors.

A large fraction of the contributions on ASICs were related to the ILC detectors, where a low material budget within the detector and low-power front-end electronics are particularly important. Developments addressing these requirements include monolithic pixel systems, ASICs to read out CCD arrays and ASICs to read out silicon microstrips in advanced 130 nm CMOS technology with built-in support for power cycling.

The ASICs being developed for particle detector readout are now becoming real “systems on chips”, and their increasing complexity requires ever more expertise from larger and larger development teams, as well as an approach that takes system aspects into account from an early stage of the development. The appropriate choice of technology will depend strongly on the specific development timescale of the different projects, as well as the global cost of accessing such technologies, including qualification and the design support environment. The use of a common technology base would allow sharing of building blocks and reduction of the global effort needed for radiation hardness qualification.

The maintenance of the firmware and the software will present a considerable support challenge over the lifetime of the experiments.

A Microelectronics Users’ Group meeting directly followed the ASIC session to spread information about progress in making deep sub-micrometre technologies available to the particle-physics community. CERN has negotiated access to 130 nm and 90 nm CMOS technologies following a similar model to that used for the 250 nm technology employed in many of the developments for LHC experiments. A design kit and a commercial library facilitating digital and mixed-signal ASIC developments in 130 nm CMOS are already available for the SLHC, ILC and other future projects.

The transmission of signals between the front-end ASICs and the readout, trigger, timing and control crates in the counting rooms of the LHC experiments has in nearly all cases been implemented with radiation-resistant high-bandwidth optical links. The production, assembly, integration and commissioning of these optical links involved large-scale quality-assurance programmes. Contributors to the workshop presented various quality-control tools for integration of optical link systems, commissioning and in-field fault diagnosis. Despite initial fears about their fragility, the quality of the systems installed so far has proved to be very high, with the fraction of unrecoverable faulty connections in the per mille range. Recently, efforts have begun to investigate the possibility of using similar optical systems at the SLHC. Although the rapid evolution of technology is making available optical links with sufficient bandwidth, effort on the selection and radiation hardness qualification of optical fibres, lasers, and pin photodiodes is just starting. Results were presented at the workshop on radiation tests of optical fibres and vertical cavity surface-emitting lasers (VCSELs) operating at 850 nm wavelength. A working group met to coordinate work on future optical systems with the aim of promoting common development, testing and qualification paths.

In parallel to the highly customized front-end electronics, impressive progress is also being made in commissioning the trigger and data-acquisition interface electronics for LHC experiments. The back-end electronics in the counting rooms typically employ large, high-density boards housing optical transceivers and several field- programmable gate arrays (FPGAs). Manufacturing problems with the high-density circuit boards have been largely overcome through close co-operation with the manufacturers and ongoing attention to detail. The use of FPGAs provides complex data-processing functionality in a reduced board area, and their reconfigurability is ideal for the flexible implementation and evolution of trigger algorithms. A downside of this flexibility is the potential proliferation of firmware versions and variants across a large number of board designs and different types of FPGA. The maintenance of the firmware and the software will present a considerable support challenge over the lifetime of the experiments.

The TWEPP ’07 workshop confirmed that most electronics systems for LHC experiments are ready and functioning according to specifications. In addition, it took a further step towards extending the original goals of the earlier Workshops on Electronics for LHC Experiments to the wider community of particle physicists engaged in developing future experimental facilities. It provided an excellent forum to exchange novel ideas, technical know-how and practical experience between different sectors of the international particle-physics community. In a context where electronics is an essential enabler for future experiments, such a forum will certainly contribute to improving the quality and reliability of the systems built. It will also lead to the formation of new collaborations and the preparation of common projects.