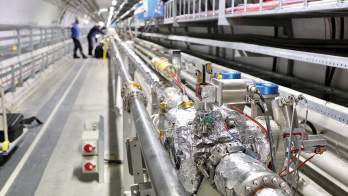

The demands that CERN’s forthcoming Large Hadron Collider (LHC) place on detectors have led the LHCb collaboration to look to Latin flair for a solution. A group from the Laboratorio de Particulas Elementares (LAPE) at the Physics Institute of Brazil’s Federal University of Rio de Janeiro (UFRJ) has been working with the CERN microelectronics group to develop readout chips for the experiment’s muon detectors.

LHCb is a collaboration dedicated to the study of CP violation, the mechanism responsible for the matter antimatter imbalance in the universe. It will do so by observing the decays of B-mesons, particles containing b quarks, emerging from high-energy proton-proton collisions in the LHC.

Since such decays frequently involve muons, the collaboration’s muon system is a key element of the detector, both for triggering and measurement purposes. LHCb’s muon detector is a combination of resistive plate chamber (RPC) and multi-wire proportional chamber (MWPC) technologies. While RPCs cover the region with a modest particle flux, MWPCs are used in a higher radiation environment, placing stringent demands on the readout electronics.

Some 600 MWPCs with a total of around 125 000 readout channels will make up the LHCb muon system. Efficiency above 99% in a 20 ns time window with rates up to 800 kHz is required, and the readout electronics must also withstand an integrated radiation dose of one megarad over the experiment’s lifetime.

This has led to the choice of quarter-micron CMOS technology, which is known for its radiation hardness when designed according to a particular layout technique, and which has been adopted by all the LHC’s experiments. LHCb’s particular requirement derives from the fact that the muon system’s readout pads cover a large range of sizes, leading to capacitances varying from 10 to 200 pF.

A preliminary chip designed by the CERN-UFRJ group, CARIOCA (CERN And RIO Current Amplifier), was tested at CERN in September. Optimized for an input capacitance of 120 pF, the CARIOCA chip has so far performed well. The time for the signal to peak rises linearly with input capacitance from a pedestal value of 14 ns to 22 ns at 120 pF, while sensitivity remains constant across the full range at around 8 mV/fC. Low noise performance has also been achieved, with 2000 electrons for a detector capacitance of 50 pF. Radiation measurements have yet to be done, but so far the CARIOCA chip’s performance is living up to expectations. A second-generation prototype is expected soon, with the goal of optimizing for an input capacitance of 200 pF.

Elsewhere in LHCb, progress is equally positive. Following the collaboration’s first technical design report (TDR), which covered the magnet and was submitted in December 1999 and approved in March, two further TDRs were submitted to the LHC Committee in September. These cover the Ring-Imaging Cherenkov counter and calorimeters.

A tender has recently been issued for the magnet, which bucks the trend in particle physics in that it is not superconducting. For LHCb, the ability to switch polarity during a run is vital to reduce systematic errors on sensitive CP-violation measurements, and that is more easily achievable with a warm magnet.

A further seven TDRs are scheduled to be submitted up to mid-2002, covering all of the remaining LHCb sub detectors. That for the muon system is scheduled for May 2001, with the final TDR covering the experiment’s computing needs to take full advantage of Moore’s Law. Like all the LHC’s experiments, LHCb is relying on computing components whose development timetable matches that of the experiment itself.